A HIGH PERFORMANCE MODULAR CCD CONTROLLER

Copyright © 2021 Semiconductor Technology Associates, Inc. 1241 Puerta Del Sol, San Clemente, CA 92673 (949) 481-1595 – http://www.sta-inc.net – <u>customerservice@sta-inc.net</u>

Revision 1.0.1166 – February 23, 2021

# **Table of Contents**

| Introduction9                                    |

|--------------------------------------------------|

| Archon Feature Summary9                          |

| Basic Operation10                                |

| Clock Driver Module11                            |

| DC Bias Modules11                                |

| ADC Module                                       |

| ADM Module12                                     |

| High Speed Clock Module13                        |

| LVDS Clock Module                                |

| Heater Module13                                  |

| HeaterX Module14                                 |

| Archon Chassis                                   |

| Backplane X1215                                  |

| Communication15                                  |

| Hardware Triggers15                              |

| Synchronization (Backplane Rev. D and earlier)18 |

| Synchronization (Backplane Rev. E and later)18   |

| Power                                            |

| Modules                                          |

| ADC Module                                       |

| ADM Module25                                     |

| Driver Module                                    |

| DriverX Module                                   |

| LVBias/LVXBias Module                            |

| HVBias/HVXBias Module                            |

| XVBias Module                                    |

| HS (High Speed) Module                           |

| LVDS Module                                      |

| Heater Module                                    |

| HeaterX Module                                   |

| System Power                                     |

| Power Consumption    | 44 |

|----------------------|----|

| Communication        | 45 |

| SYSTEM               | 46 |

| STATUS               | 47 |

| TIMER                | 49 |

| FRAME                | 50 |

| FETCHLOG             | 50 |

| LOCKn                | 50 |

| VERIFYMODxxyyyyzzzz  | 50 |

| ERASEMODxx           | 50 |

| FLASHMODxxyyyyzzzzzz | 50 |

| ERASExxxxxxxyyyyyyyy | 50 |

| FLASHxxxxyyyyyy      | 51 |

| VERIFYxxxxyyyy       | 51 |

| REBOOT               | 51 |

| WARMBOOT             | 51 |

| FETCHxxxxxxxyyyyyyyy | 51 |

| WCONFIGxxxxtttttt    | 51 |

| RCONFIGxxxx          | 51 |

| CLEARCONFIG          | 51 |

| APPLYALL             | 51 |

| POWERON              | 51 |

| POWEROFF             | 51 |

| LOADTIMING           | 51 |

| LOADPARAMS           | 52 |

| LOADPARAM p          | 52 |

| PREPPARAM p          | 52 |

| FASTLOADPARAM p d    | 52 |

| FASTPREPPARAM p d    | 52 |

| RESETTIMING          | 52 |

| HOLDTIMING           | 52 |

| RELEASETIMING        | 52 |

| APPLYMODxx        | 52 |

|-------------------|----|

| APPLYDIOxx        | 53 |

| APPLYSYSTEM       | 53 |

| APPLYCDS          | 53 |

| FLASHACTIVECONFIG | 53 |

| ERASESTOREDCONFIG | 53 |

| APPLYNET          | 53 |

| Configuration     | 54 |

| IP                | 54 |

| PORT              | 54 |

| LINECOUNT         | 54 |

| LINES             | 55 |

| LINEn             | 55 |

| STATES            | 55 |

| STATEn/NAME       | 55 |

| STATEn/CONTROL    | 55 |

| STATEn/MODi       | 55 |

| PARAMETERS        | 55 |

| PARAMETERn        | 55 |

| CONSTANTS         | 55 |

| CONSTANTn         | 55 |

| SHP1              | 55 |

| SHP2              | 55 |

| SHD1              | 55 |

| SHD2              | 55 |

| BIGBUF            | 55 |

| RAWENABLE         | 56 |

| RAWSEL            | 56 |

| RAWSTARTLINE      | 56 |

| RAWENDLINE        | 56 |

| RAWSTARTPIXEL     | 56 |

| RAWSAMPLES        | 56 |

| SAMPLEMODE         | 56 |

|--------------------|----|

| PIXELCOUNT         | 56 |

| FRAMEMODE          | 56 |

| LINESCAN           | 56 |

| TAPLINES           | 56 |

| TAPLINEn           | 56 |

| TRIGOUTFORCE       | 56 |

| TRIGOUTLEVEL       | 56 |

| TRIGOUTINVERT      | 57 |

| TRIGOUTPOWER       | 57 |

| TRIGINENABLE       | 57 |

| TRIGININVERT       | 57 |

| EXTCLOCK           | 57 |

| FANDISABLE         | 57 |

| APPLYALL           | 57 |

| POWERON            | 57 |

| MODm/LABELi        | 57 |

| MODm/FASTSLEWRATEi | 58 |

| MODm/SLOWSLEWRATEi | 58 |

| MODm/ENABLEi       | 58 |

| MODm/SOURCEi       | 58 |

| MODm/CLAMPHIGH     | 58 |

| MODm/CLAMPLOW      | 58 |

| MODm/CLAMP1        | 58 |

| MODm/CLAMP2        | 58 |

| MODm/CLAMP3        | 58 |

| MODm/CLAMP4        | 59 |

| MODm/PREAMPGAIN    | 59 |

| MODm/LVLC_LABELi   | 59 |

| MODm/LVHC_LABELi   | 59 |

| MODm/LVLC_Vi       | 59 |

| MODm/LVLC_ORDERi   | 59 |

| MODm/LVHC_Vi           | 59 |

|------------------------|----|

| MODm/LVHC_ORDERi       | 59 |

| MODm/LVHC_ENABLEi      | 59 |

| MODm/LVHC_ILi          | 59 |

| MODm/HVLC_LABELi       | 59 |

| MODm/HVHC_LABELi       | 59 |

| MODm/HVLC_Vi           | 59 |

| MODm/HVLC_ORDERi       | 59 |

| MODm/HVHC_Vi           | 60 |

| MODm/HVHC_ORDERi       | 60 |

| MODm/HVHC_ENABLEi      | 60 |

| MODm/HVHC_ILi          | 60 |

| MODm/HEATERxENABLE     | 60 |

| MODm/HEATERxFORCE      | 60 |

| MODm/HEATERxFORCELEVEL | 60 |

| MODm/HEATERxLIMIT      | 60 |

| MODm/HEATERxTARGET     | 60 |

| MODm/HEATERxSENSOR     | 60 |

| MODm/HEATERxSENSORTYPE | 60 |

| MODm/SENSORxTYPE       | 60 |

| MODm/SENSORxCURRENT    | 61 |

| MODm/SENSORxLOWERLIMIT | 61 |

| MODm/SENSORxUPPERLIMIT | 61 |

| MODm/SENSORxFILTER     | 61 |

| MODm/HEATERxP          | 61 |

| MODm/HEATERxI          | 61 |

| MODm/HEATERxIL         | 61 |

| MODm/HEATERxD          | 61 |

| MODm/HEATERUPDATETIME  | 61 |

| MODm/HEATERxRAMP       | 61 |

| MODm/HEATERxRAMPRATE   | 61 |

| MODm/HEATERxLABEL      | 61 |

| MODm/SENSORxLABEL          | 62 |

|----------------------------|----|

| MODm/DIO_LABELi            | 62 |

| MODm/DIO_SOURCEi           | 62 |

| MODm/DIO_DIRi              | 62 |

| MODm/DIO_POWER             | 62 |

| MODm/VCPU_LINES            | 62 |

| MODm/VCPU_LINEi            | 62 |

| MODm/VCPU_INREGi           | 62 |

| MODm/HS_LABELi             | 62 |

| MODm/MAG_LABELi            | 62 |

| MODm/HS_LABELi             | 62 |

| MODm/MAG_Vi                | 62 |

| MODm/OFS_Vi                | 63 |

| MODm/LVDS_LABELi           | 63 |

| MODm/XVP_LABELi            | 63 |

| MODm/XVN_LABELi            | 63 |

| MODm/XVP_Vi                | 63 |

| MODm/XVN_Vi                | 63 |

| MODm/XVP_ENABLEi           | 63 |

| MODm/XVN_ENABLEi           | 63 |

| MODm/XVP_ORDERi            | 63 |

| MODm/XVN_ORDERi            | 63 |

| Timing Core                | 64 |

| Instructions               | 64 |

| Timing Script              | 65 |

| Timing Core States         | 67 |

| Sampling and Deinterlacing | 69 |

| Raw Samples                | 70 |

| Frame Buffers              | 71 |

| GUI                        | 72 |

| System Tab                 | 74 |

| Timing Script Tab          | 74 |

| Timing States Tab7                           | 5 |

|----------------------------------------------|---|

| Parameters Tab7                              | 5 |

| VCPU Tab7                                    | 6 |

| CDS/Deint Tab7                               | 6 |

| Image Tab7                                   | 6 |

| Plot Tabs7                                   | 7 |

| Raw Tabs7                                    | 7 |

| ADC Tab7                                     | 7 |

| Driver Tab7                                  | 7 |

| Bias Tabs7                                   | 7 |

| Basic Examples                               | 8 |

| Grounding                                    | 5 |

| VCPU                                         | 6 |

| VCPU Programs8                               | 6 |

| VCPU Op-codes                                | 7 |

| VCPU I/O                                     | 0 |

| VCPU Sample Program9                         | 1 |

| Appendix A: Test Clock Configuration File9   | 5 |

| Appendix B: Basic Example Configuration File | 9 |

# Introduction

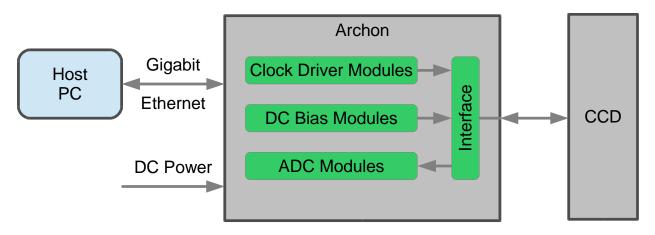

Archon is a high performance modular CCD controller developed by Semiconductor Technology Associates, Inc (STA). This manual provides an overview of the controller followed by detailed descriptions of the hardware and software. A top level block diagram is shown in Figure 1.

#### Figure 1: Top Level Block Diagram

An Archon system receives configuration information from and sends status and image data to a host PC via a gigabit Ethernet connection (either copper or fiber). Power is supplied to Archon through a circular connector carrying the DC voltages necessary for a particular system, or through a standard AC power cord for Archon AC. The CCD to be operated is connected to Archon through a custom interface board, built to route signals from the CCD cabling to the internal Archon module connectors.

#### **Archon Feature Summary**

- Compact size: Standard chassis is 11.5" x 8" x 4.5" (29.21 x 20.32 x 11.43 cm), Archon AC chassis is 11.5" x 8" x 7".

- Modular: 12 slots for ADC, clock driver, bias, heater, or other custom modules

- Dense: Up to 4 ADC modules for 16 total CCD outputs

- Low weight: 8.5 lbs (3.9 kg) for a typical 4 channel system, 17.5 lbs (8kg) for a 16 channel Archon AC system

- Low power: 41 W for a typical 4 channel system, 89W for a 16 channel Archon AC system

- High dynamic range: 108 dB at 100 kHz, 98 dB at 1 MHz using 16 or 32 bits per sample

- Easy interfacing: standard gigabit network interface, either copper or fiber SFP module

- On-board frame buffer: 2GB RAM for flexible readout

- Timing core: 100 MHz master clock for 10 ns timing resolution

- ADC Module: 4 fully differential AC-coupled 100 MHz 16 bit channels using digital CDS, and software selectable 1.33 V or 4 V input range

- ADM Module: 18 fully differential DC-coupled 12.5 MHz 18 bit channels using digital CDS, and a 6 V input range

- Clock Driver Module: 8 or 12 channels of 100 MHz 14-bit DACs for generating slew-rate controlled, multi-level clocks from -13.000...+13.000 V

- Low Voltage Bias Module: 30 total biases at -14.000...+14.000 V, with 6 high power channels supplying up to 500 mA each (programmable current limit), and 24 low power channels supplying up to 10 mA each (1 A max total current per module)

- High Voltage Bias Module: 30 total biases at 0.000...+31.000 V, with 6 high power channels supplying up to 250 mA each (programmable current limit), and 24 low power channels supplying up to 10 mA each (1 A max total current per module)

- XV Bias Module: 4 channels at 0.000...+95.000 V and 4 channels at -95.000...0.000, each supplying up to 50 mA

- HeaterX Module: Two 25W heater drivers (intended for 25 Ohm resistors) and three temperature sensor channels, with programmable excitation currents from 25 nA to 1.5 mA

- High Speed Clock Module: 12 channels of LVDS clocks with 1 ns resolution, 12 clock magnitudes from 5.000...14.000V (up to 1A each), 12 clock offsets from -14.000V...+14.000V (10 mA each)

- LVDS Clock Module: 16 channels of LVDS clocks with 10 ns resolution, +3.3V, +/-5V, +/-16V supplies (1A each)

- Digital I/O: General purpose digital I/O lines powered internally or externally are on the LVBias, Heater, HS and LVDS modules (8 lines on LVBias/Heater, 4 lines on HS/LVDS)

- Programmable I/O: Modules with digital I/O lines contain real time 16-bit CPUs that can be user programmed for interface tasks

- All biases monitor current and voltage

- Triggering: opto-isolated BNC input and output

- Synchronization: multiple controllers can be synchronized over dedicated Cat5 cable

- Software: example GUI application provided with source for Windows/Linux/OSX

- Temperature: operating range -20C to +40C

### **Basic Operation**

High level system configuration is accomplished by a 32-bit CPU embedded in the Archon backplane master FPGA. This CPU communicates with an upstream host (typically a data capture computer) via gigabit Ethernet using a human-readable serial text stream of commands and responses. The 32-bit CPU translates high level camera configuration commands from the host (bias voltages, clock timing, etc.) into low level commands for the FPGAs on each installed module (DACs, ADCs, etc).

The clock sequences needed to read out a CCD are generated by timing cores embedded in each FPGA. The backplane supplies a master 100 MHz clock to all timing cores. The timing cores are simple processors/state machines, with an instruction set composed of NOPs, GOTOs, CALLs, and RETURNs. Each instruction executes in a single master clock cycle (10 ns). Instruction execution can be conditional on user-set parameters. The call stack allows subroutines to be nested 16 deep. Each instruction in memory has an associated set of output signals for that clock state specific to a particular module, including clock voltage levels, clamp and sample timing for the ADCs, and triggers.

### **Clock Driver Module**

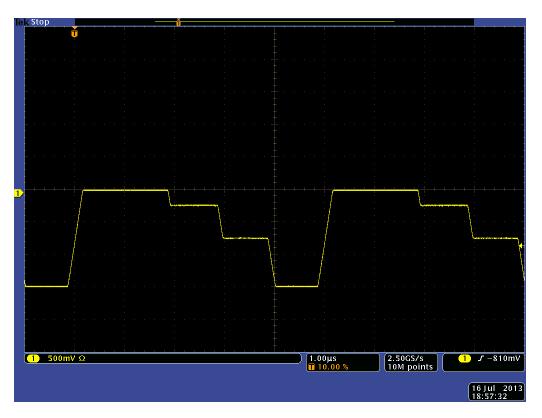

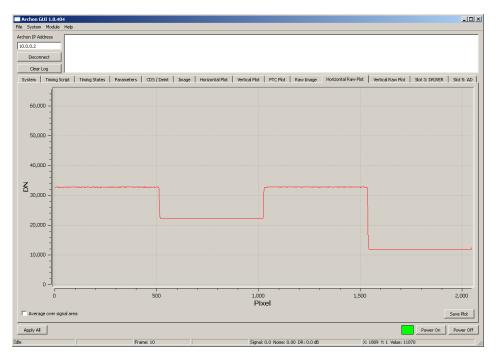

Each clock driver module has 8 channels (or 12 for DriverX) of 100 MHz 14-bit DACs, with output swings of -13.000 V to +13.000 V (~2 mV resolution). Every clock driver has a target voltage that is set at each 10 ns clock tick. Each clock slews towards its current target at a selectable fast or slow rate. The fast and slow slew rates are configurable per channel, and the slew rate can be changed to fast or slow at each clock tick. This flexibility makes it possible to extract maximum performance from a CCD. For example, a CCD area clock could be programmed to slew slowly from inversion to a voltage just out of inversion, followed by a fast slew to its nominal high level, minimizing spurious charge and maximizing the readout rate. The same clock could then go to a very high voltage during integration to optimize MTF. The clock drivers have a series 50 ohm resistor, which is usually the limiting factor for the maximum slew rate when driving heavy capacitive loads. For light loads, the 10% to 90% time for a 10V swing is typically 22 ns at the maximum slew rate.

#### **DC Bias Modules**

Each bias module provides 30 programmable DC biases, 0.000 to +31.000 V for the HVBias module, and -14.000 to +14.000 V for the LVBias module. On each bias module, there are 6 high power (250 mA HV, 500 mA LV) biases and 24 low power (10 mA) biases. The high power biases have programmable current limits. Note that while each high power bias is rated for 250/500 mA, the combined current from all biases on a single module cannot exceed 1A. The current and voltage of each bias is monitored, both for calibration when the bias is set and to assist in debugging system faults.

The XV bias module provides 8 programmable DC biases, with four channels that range from 0.000 to +95.000 V, and four channels that range from -95.000 to 0.000 V. Each channel can supply up to 50 mA. The current and voltage of each bias is monitored, both for calibration when the bias is set and to assist in debugging system faults.

The biases start at OV. When a "Power On" command is given, the biases rise to their nominal levels. The power-up sequence can be controlled by assigning a step number to each bias. Step 1 biases will go to their target values first. Their levels will be checked, and then step 2 biases will come up, and so on until all biases are at their nominal voltages. During a power down, the sequence is reversed. This is useful for CCDs that require particular power-up sequences to avoid damage. All of the clock drivers and biases are isolated from the CCD by solid state relays. Beyond the relays are weak (100k, 1M on XVBias) resistors to ground. The relays only connect the biases and clocks to the CCD when all Archon power supplies are at nominal levels and the FPGA has commanded the relays to engage. If the FPGA is reset, or one the system power supplies goes bad, the relays are opened and will not close again until the system has been reconfigured.

The LVBias module additionally has 8 general purpose digital I/Os, which can be powered by an internal +3.3V or by an external supply from +1.65V to +5.5V. Each group of 2 I/Os can be configured as inputs or outputs. When an output, each line can be driven high, low, or by the timing core. In addition, the digital I/O lines can be controlled by a dynamically programmable embedded 100 MHz 16-bit CPU for simple interface tasks, such as communication with an RS-232 vacuum gauge or I2C temperature sensor.

Improved versions of the bias modules have been introduced, called the HVX and LVX bias modules. They have identical functionality to the standard bias modules, but add additional buffering that enables much faster background bias polling. Note that the new extended bias modules are longer than standard modules, and can only be installed in slots 3-4 and slots 9-12.

#### **ADC Module**

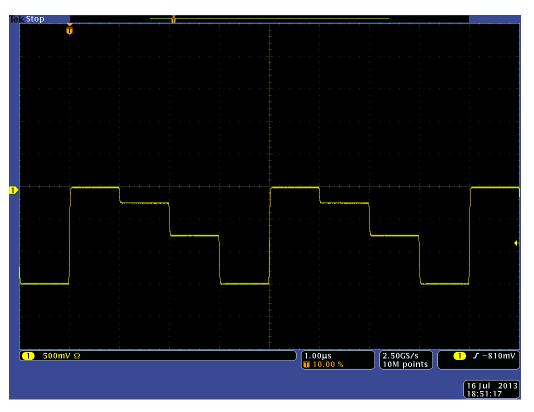

Each ADC module has four 100 MHz 16-bit channels with preamps, designed for CCD pixel clocks of up to 3 MHz. Up to four ADC modules can be installed in an Archon chassis. The preamps are fully differential and AC-coupled. The preamp gain is software selectable, and can be set for either a 4V or 1.33V full scale input. Because the preamps are AC-coupled, an integrated DC-restore clamp must be activated periodically. Clamping is usually done once per line, either during overscan pixels or during the vertical transfer. The clamp level is programmable to map the CCD reset level near the top of the ADC range. Correlated double sampling (CDS) is performed digitally in the FPGA, which allows multiple reset and video levels to be averaged, driving noise down as the pixel clock is reduced. For typical CCD timings at high gain (full scale ≈ 1.33V), noise is 0.79 DN (16 uV RMS) at a 1 MHz pixel clock with a grounded input, and 0.28 DN (5.7 uV RMS) at 100 kHz. At low gain (full scale  $\approx$  4V), noise is 0.66 DN (40 uV RMS) at a 1 MHz pixel clock with a grounded input, and 0.24 DN (15 uV RMS) at 100 kHz. The previous values assume 16 bits per pixel. Digitizing signals with noise less than the equivalent of 0.5 DN at 16 bits requires additional bits per pixel. 32 bits per pixel can be acquired in the controller's high dynamic range mode. In addition to the normal CDS pixel data, portions of the raw ADC data can be simultaneously captured to a memory buffer. This allows a detailed, low-noise oscilloscope view of the CCD output waveform during device tuning. The raw waveforms simplify the examination of clock feedthrough, reset level stability, and optimal CDS sample points.

#### **ADM Module**

Each ADM module has eighteen 12.5 MHz 18-bit channels with preamps, designed for pixel clocks of up to 5 MHz. Up to four ADM modules can be installed in an Archon chassis. The preamps are fully differential and DC-coupled. The input range is 6V (+3V to -3V differential). Correlated double sampling (CDS) is performed digitally in the FPGA, which allows multiple reset and video levels to be averaged, driving noise down as the pixel clock is reduced. For a grounded input with 200kHz timings, noise is 0.13DN (11uV RMS). The ADM modules use Archon's normal 100MHz 16 bit data path to the CDS processor. To accomplish this, an 18 bit sample is truncated to 16 bits, and replicated 8 times. The truncated 16 bits are then dithered during those 8 sample periods so CDS averaging will recover the original 18 bit value. In addition to the normal CDS pixel data, portions of the raw ADC data can be simultaneously captured to a memory buffer. This allows a detailed, low-noise oscilloscope view of the CCD output waveform during device tuning. The raw waveforms simplify the examination of clock feedthrough, reset level stability, and optimal CDS sample points.

### **High Speed Clock Module**

The high speed clock modules are intended to drive external high speed clock buffers. There are 12 high speed channels. Each channel has an LVDS output with 1 ns timing resolution. Each channel also has a clock magnitude programmable from 5V to 14V capable of sourcing 1A, and a clock offset programmable from -14V to + 14V that can source/sink 10 mA. Each clock magnitude and offset is monitored for voltage and current. Clock magnitudes and offsets power on and off at step 1 of the power sequence.

The high speed clock module additionally has 4 general purpose digital I/Os, which can be powered by an internal +3.3V or by an external supply from +1.65V to +5.5V. Each I/O can be configured as an input or an output. When an output, each line can be driven high, low, or by the timing core. In addition, the digital I/O lines can be controlled by a dynamically programmable embedded 100 MHz 16-bit CPU for simple interface tasks, such as communication with an RS-232 vacuum gauge or I2C temperature sensor.

#### **LVDS Clock Module**

The LVDS clock modules are intended to drive external high speed clock buffers. There are 16 LVDS channels with 10 ns timing resolution. +3.3V, +/-5V, and +/-16V supplies are also provided. The supplies power on and off at step 1 of the power sequence.

The LVDS clock module additionally has 4 general purpose digital I/Os, which can be powered by an internal supply of +3.3V or by an external supply from +1.65V to +5.5V. Each I/O can be configured as an input or an output. When an output, each line can be driven high, low, or by the timing core. In addition, the digital I/O lines can be controlled by a dynamically programmable embedded 100 MHz 16-bit CPU for simple interface tasks, such as communication with an RS-232 vacuum gauge or I2C temperature sensor.

#### **Heater Module**

Each heater module has two output channels, intended to source up to 1A each at up to 25V while driving a heater element (typically 25 ohms). There are also two temperature monitoring channels, which source precisely 10 uA each and are intended to monitor silicon diode temperature sensors via a four wire force/sense interface. A PID loop can be used to drive either heater output based on either temperature input. Heater power is taken from a dedicated line on the Archon power connector for flexibility.

The heater module additionally has 8 general purpose digital I/Os, which can be powered by an internal +3.3V or by an external supply from +1.65V to +5.5V. Each group of 2 I/Os can be configured as inputs or outputs. When an output, each line can be driven high, low, or by the timing core. In addition, the digital I/O lines can be controlled by a dynamically programmable embedded 100 MHz 16-bit CPU for simple interface tasks, such as communication with an RS-232 vacuum gauge or I2C temperature sensor.

#### **HeaterX Module**

The HeaterX module is an upgrade to the Heater module. It has the same two 25W heater outputs, but has three temperature monitoring channels with precision current sources programmable from 25 nA to 1.5 mA in 25 nA steps, compatible with silicon diodes or RTDs.

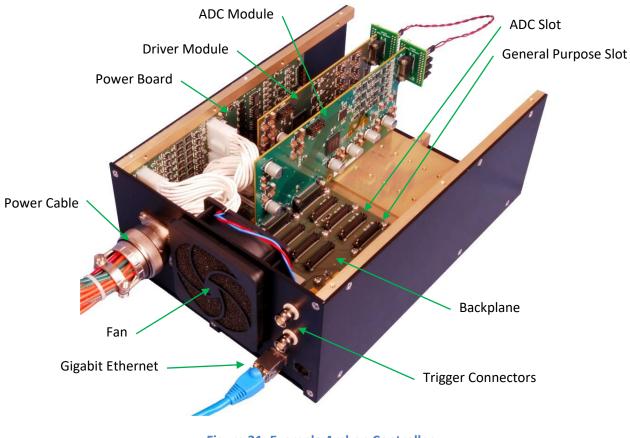

### **Archon Chassis**

The Archon chassis is built from aluminum, with electrically conductive chem film internal surfaces for shielding, and anodized external surfaces for durability. An 80mm fan with filter on the rear face cools the internal components with ambient air, which is channeled past the modules and then exhausted through ducts on the same face as the fan intake. The front face is customized to accommodate the connectors needed for a particular CCD.

Power for the standard chassis is supplied as a set of DC voltages through a circular bayonet connector. The DC supply lines pass through a power conditioning board, which keeps the power lines disconnected from the rest of the system until all voltages are at their nominal values. The voltages necessary for a particular system vary depending on the installed modules. Jumpers on the power conditioning board allow the user to select which voltages should be monitored for a system. Linear or switching external power supplies can be used to generate the system DC voltages, depending on a particular application's need for low noise or high efficiency.

The Archon AC chassis uses a standard IEC AC power cable, and has internal DC-DC converters. The Archon AC chassis also comes with an integrated water block with 3/8" (9.5mm) copper tubing for optional liquid cooling, and the fan can be disabled in software.

# **Backplane X12**

The Archon backplane is responsible for communication with the host system, along with communication and power distribution for the installed modules. The X12 variant can support 12 installed modules, of which 4 can be ADC modules. Processing is done by a 32-bit soft processor embedded in the backplane Kintex 7 FPGA for older systems, and by a 64-bit ARM processor for Rev H backplanes. The CPU has 2 GB of DDR3 RAM, with 512 MB reserved for the processor and three 512 MB frame buffers. 16 MB of flash memory stores firmware and controller configuration data.

#### **Communication**

All communication goes through the onboard FPGA. The embedded CPU communicates with an upstream host system through an SFP socket, which can be populated with either a fiber or copper gigabit Ethernet module. Rev H backplanes have a dedicated copper gigabit ethernet port, with an additional SFP socket which supersedes the copper interface when populated with a fiber SFP module. Note that the socket communicates only at a gigabit rate; it is not backward compatible with 10 or 100 megabit networks. The CPU listens for a TCP/IP connection on port 4242 to initiate communication. Rev F and older backplanes can only support a single connection at a time. For this reason, and to avoid network contention, the Archon controller is normally connected to a dedicated network port on the host system. Rev H backplanes currently support up to four simultaneous connections.

#### **Hardware Triggers**

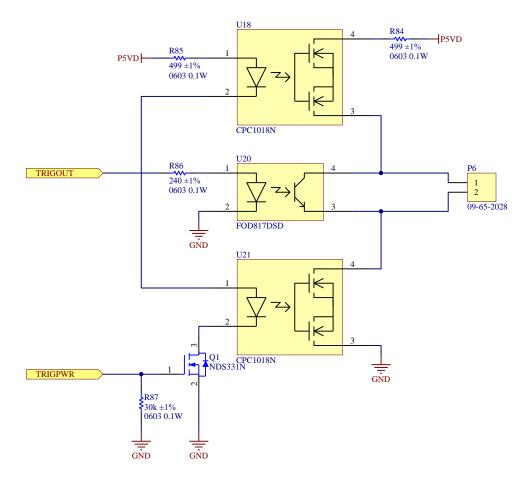

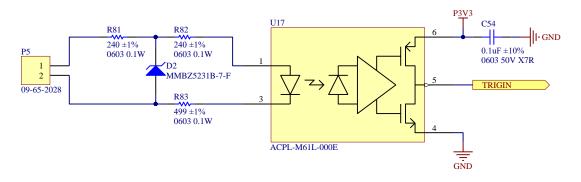

The backplane has connections to two BNC connectors on the chassis, Trigger Out and Trigger In. The electronic Trigger Out interface is shown in Figure 2. The output can be optoisolated, or optionally directly driven with a 499 ohm pull-up to 5V on the positive line and the negative line tied to ground. Refer to the FOD817 datasheet for specific performance information for the optoisolator. In general, the output will sink 10 mA with a saturation voltage < 0.5V when on. The Trigger Out signal can be forced high or low, or connected to a timing core clock (the INT control signal, for exposure integration time). This is typically used to drive a shutter or light source.

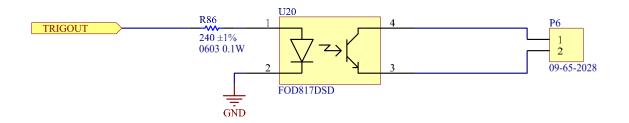

Rev F and newer versions of the backplane have separate optoisolated and driven Trigger Out circuits that are selected by connecting the Trigger Out cable to the desired header, as seen in Figure 3.

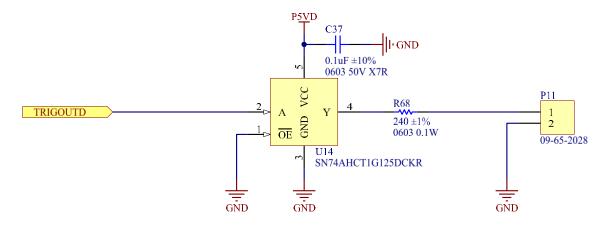

The Trigger In circuit is shown in Figure 4. A 3.3V input at 2 mA is sufficient to trigger the optoisolator. Inputs up to 10V are tolerated. The Trigger In signal can be connected to the timing core reset input. This is typically used to trigger a new frame.

Figure 2: Trigger Out Schematic (Rev E and earlier)

Figure 3: Trigger Out Schematic (Rev F and later)

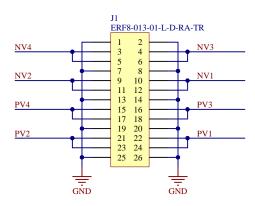

### Synchronization (Backplane Rev. D and earlier)

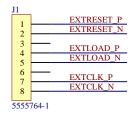

The Sync RJ-45 jack on the backplane is provided to facilitate the synchronization of multiple Archon controllers. The external synchronization interface consists of 3 LVDS receiver pairs, with 110 Ohm internal termination. The connector pinout is shown in Figure 5. EXTCLK is routed to a PLL which generates the master 100.0 MHz clock from either an internal 25.0 MHz clock or from EXTCLK when in external master clock mode. EXTRESET and EXTLOAD are connected to the RESET and LOAD signals for all timing cores in external master clock mode.

Figure 5: Sync Connector

To synchronize multiple systems, an external 25.0 MHz LVDS clock must be applied to EXTCLK. Hold EXTRESET high, apply the desired system configurations (including configuration key "EXTCLOCK = 1") to all systems, and then release EXTRESET. All controllers will then begin executing their timing scripts synchronously. To synchronously update a timing parameter, issue the "PREPPARAM" command to all systems, and then pulse the EXTLOAD signal. All controllers will remain in lockstep indefinitely under these conditions. Note that removing EXTCLK from a controller while in external master clock mode will cause the system to hang. The controller will reboot if the clock is reconnected, and need to be reconfigured.

### Synchronization (Backplane Rev. E and later)

Rev. E and later Backplanes were designed to allow either daisy-chained or star topology controller synchronization. Two RJ-45 connectors (SYNCIN/J1 and SYNCOUT/J2) are provided on the backplane for synchronization of multiple Archon controllers. The synchronization interface consists of 3 LVDS pairs. The SYNCIN receivers have 110 Ohm internal termination. The connector pinouts are shown in Figure 6. EXTCLK is routed to a PLL which generates the master 100.0 MHz clock from either an internal 100.0 MHz clock or from EXTCLK when an external 100.0 MHz clock is detected. EXTRESET and EXTLOAD are connected to the RESET and LOAD signals for all timing cores when an external clock is present.

**Figure 6: Sync Connector**

INTCLK, INTRESET, and INTLOAD are driven by EXTCLK, EXTRESET, and EXTLOAD when an external clock is present, or by the internal 100.0 MHz clock, RESET, and LOAD signals when no external clock is detected. To synchronize multiple systems in a daisy chain, connect standard Cat-5 network cables from the SYNCOUT of each system to the SYNCIN of the next system. The first system in the chain (the master) will have no SYNCIN connection, and the last system in the chain will have no SYNCOUT connection. Keep all timing cores in reset (Give the "HOLDTIMING" command to either the master or all systems). Apply the desired system configurations to all systems. Release the timing cores from reset using "RELEASETIMING". All controllers will then begin executing their timing scripts synchronously. Note that there is a static delay between systems of about 10 ns plus cable propagation delay. To synchronously update a timing parameter, issue the "PREPPARAM" command to all systems, and then give the "LOADPARAM" command (either to the master system or all systems). All controllers will remain in lockstep indefinitely under these conditions. Note that unplugging the sync cables during operation may cause the system to hang. The controller will reboot if the clock is reconnected, and will need to be reconfigured.

If it's necessary to eliminate the static delay associated with the daisy chain topology, it is also possible to build a simple "sync box" that outputs a common 100.0 MHz clock, RESET, and LOAD signal to all controllers in a star topology.

#### **Power**

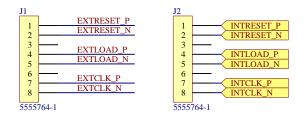

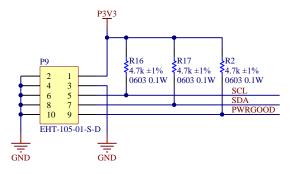

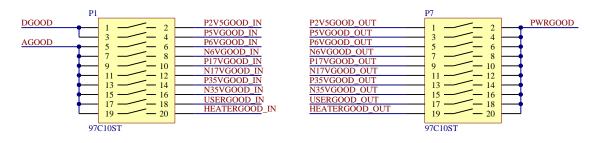

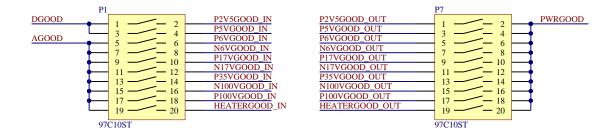

Power is supplied to the backplane through two power connectors. The pinout is shown in Figure 7. The 2.5V and 5V inputs are required to power the backplane. The other voltages need only be applied if installed modules require them. Typically, the power board (described later) monitors and gates the supply voltages and passes them to these connectors once all are at nominal levels. The backplane communicates with the power board via an IDC cable connected to P9, with the pinout shown in Figure 8.

**Figure 7: Power Connectors**

**Figure 8: Power Communication**

#### **Modules**

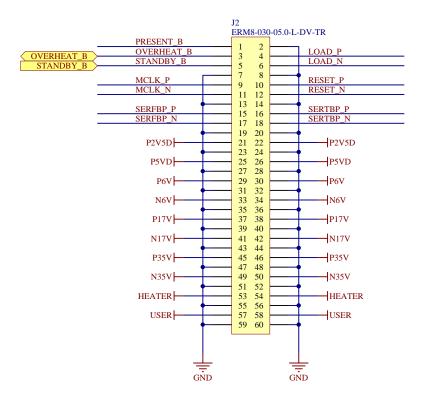

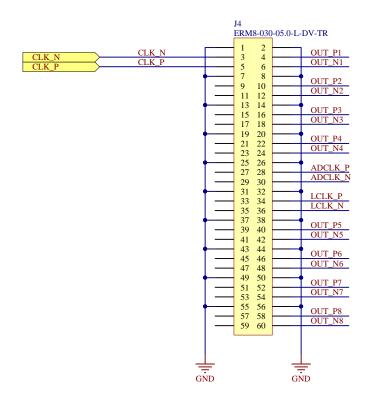

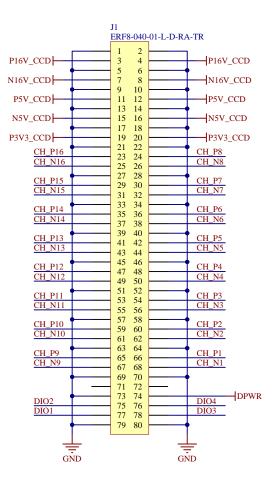

12 modules can be installed on the backplane. Most modules can be installed in any slot. The HVX Bias, LVX Bias, and HS modules are exceptions, and can only be installed in slots 3-4 or 9-12 because of their extended length. ADC modules can only be installed in the central 4 slots (5-8), which have an additional connector that carries the high speed ADC data. The module connector pinout is shown in Figure 9. A module indicates that it's installed by grounding the PRESENT signal. A module indicates that it is overheating by pulling the OVERHEAT signal low. A module is commanded to power down when the STANDBY input is low. The 100 MHz master clock is supplied to the modules on the MCLK LVDS pair. Timing core resets are commanded by RESET, and timing core parameter loads by LOAD. Serial communication between the module and the backplane is done over the SERFBP and SERTBP LVDS pairs at 6.25 Mbps. The ADC module connector is shown in Figure 10. The ADC modules are given a low jitter 100 MHz clock on the CLK pair, and transmit back a 400 MHz clock on LCLK, a framing clock on ADCLK, and sampled data bits on the OUT pairs.

**Figure 9: Module Backplane Connector**

Figure 10: ADC Module Backplane Connector

### **ADC Module**

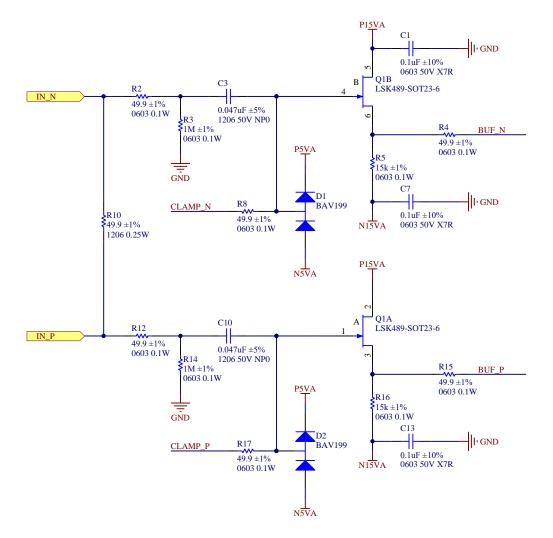

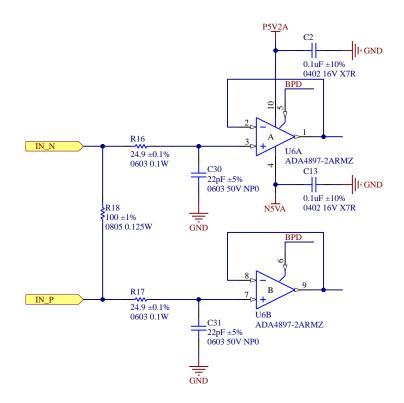

The ADC module simultaneously samples four fully differential inputs at 16 bits and 100 MHz. The raw samples are transmitted to the backplane for digital CDS processing. The input buffer is shown in Figure 11. By default, R10 is not installed. A single-ended or differential termination resistor could be installed there, or a load resistor for a JFET buffer near the CCD output. The CLAMP\_P and CLAMP\_N biases are generated by DACs, and are connected through analog switches to reset the DC level of the Q1 JFETs (typically once per line). The clamp levels are normally chosen to set the DC differential input voltage near the top of the ADC input range.

The preamp stages following Q1 have two selectable gain settings, set by resistors. The default gain resistors set the full scale differential input swing to either 1.3V or 4V, but can be modified if necessary for a particular user application. Measured low gain is 65.8 uV/DN (4.31V full scale). Measured high gain is 21.9 uV/DN (1.43V full scale). There is a low-pass filter before the ADC with a time constant of 10 ns (-3dB at 15 MHz).

Figure 11: ADC Input Buffer

The ADC module requires the P6V, N6V, P17V and N17V system supplies. The pinout for the ADC module connector is shown in Figure 12.

Figure 12: ADC Module Connector

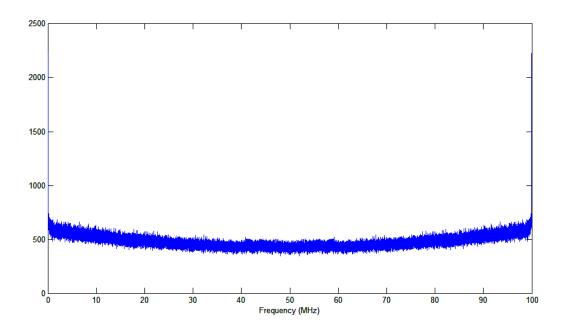

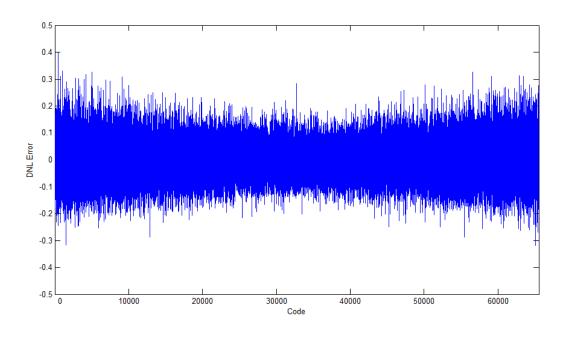

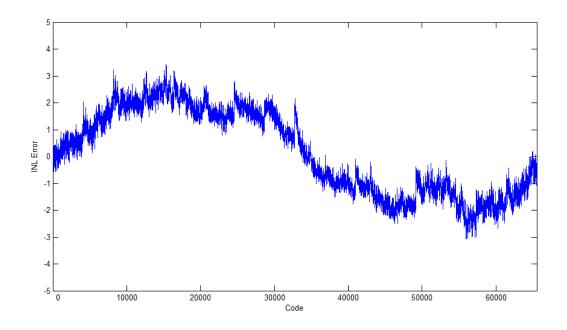

ADC module performance measurements:

- Grounded input noise (high gain, 100 MHz): 2.6 DN

- Grounded input noise (low gain, 100 MHz): 2.2 DN

- Channel to channel crosstalk: -101 dB (worst case, measured with 45000 DN signal on one channel, other channels grounded)

- Grounded input FFT:

Figure 13: ADC Grounded Input FFT

Figure 14: ADC DNL

Figure 15: ADC INL

### **ADM Module**

The ADM module simultaneously samples eighteen fully differential inputs at 18 bits and 12.5 MHz. The raw samples are transmitted to the backplane for digital CDS processing. The input buffer is shown in Figure 16. By default, R18 is not installed. A single-ended or differential termination resistor could be installed there. The full scale differential input swing is 6V, but can be modified if necessary for a particular user application. Measured gain is 91.5 uV/DN. There is a low-pass filter before the ADC with a time constant of 4.5 ns (-3dB at 35 MHz).

#### Figure 16: ADM Input Buffer

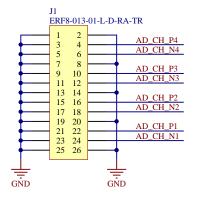

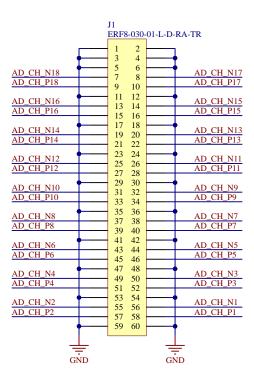

The ADM module requires the P6V and N6V system supplies. The pinout for the ADM module connector is shown in Figure 17.

**Figure 17: ADM Module Connector**

# **Driver Module**

Each clock driver module generates 8 CCD clocks using 14-bit 100 MHz DACs, with outputs ranging from -13.000 V to +13.000 V. Clock levels can be set with a resolution of about 2 mV. The timing core in the clock driver FPGA generates a new target clock level every 10 ns. The DAC outputs linearly slew toward the new target at a software selectable fast or slow rate, yielding clean trapezoidal CCD waveforms.

The output amplifier for each clock is a THS3095, rated for 250 mA. There is a series 49.9 Ohm resistor after each THS3095, which is usually the limiting factor for slew rate with heavy capacitive loads. There is also an optoisolator between each clock and the output connector. Initially, the optoisolators are open, and the pin on the output is connected to ground through a 100k resistor. When the system is configured, each clock is calibrated. When the system is commanded to enable power to the CCD, all clocks go to their initial levels, and the optoisolators are closed after the last step of the power sequence.

The system supplies are continuously monitored in hardware by comparators. In the event a system supply leaves its normal operating range, all optoisolators to the CCD are opened.

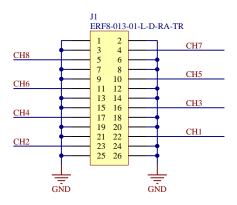

The driver module requires the P6V, N6V, P17V and N17V system supplies. The driver module pinout is shown in Figure 18.

For firmware > 1090, the clock pattern source for each clock channel can be chosen from the 8 timing core channel outputs. This means that if a CCD clock S1 was on channel 1, and S2 was on channel 2, serial clocking could be reversed by assigning channel 1 to timing core output 2 and vice -versa, with no other timing modifications necessary.

Figure 18: Clock Driver Module Connector

# **DriverX Module**

Each DriverX module generates 12 CCD clocks using 14-bit 100 MHz DACs, with outputs ranging from - 13.000 V to +13.000 V. Clock levels can be set with a resolution of about 2 mV. The timing core in the clock driver FPGA generates a new target clock level every 10 ns. The DAC outputs linearly slew toward the new target at a software selectable fast or slow rate, yielding clean trapezoidal CCD waveforms.

The output amplifier for each clock is a THS3095, rated for 250 mA. There is a series 49.9 Ohm resistor after each THS3095, which is usually the limiting factor for slew rate with heavy capacitive loads. There is also an optoisolator between each clock and the output connector. Initially, the optoisolators are open, and the pin on the output is connected to ground through a 100k resistor. When the system is configured, each clock is calibrated. When the system is commanded to enable power to the CCD, all clocks go to their initial levels, and the optoisolators are closed after the last step of the power sequence.

The system supplies are continuously monitored in hardware by comparators. In the event a system supply leaves its normal operating range, all optoisolators to the CCD are opened.

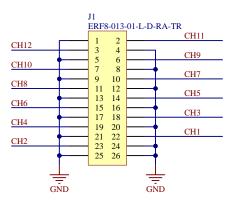

The driver module requires the P6V, N6V, P17V and N17V system supplies. The driver module pinout is shown in Figure 19.

The clock pattern source for each clock channel can be chosen from the 12 timing core channel outputs. This means that if a CCD clock S1 was on channel 1, and S2 was on channel 2, serial clocking could be reversed by assigning channel 1 to timing core output 2 and vice -versa, with no other timing modifications necessary.

Figure 19: DriverX Module Connector

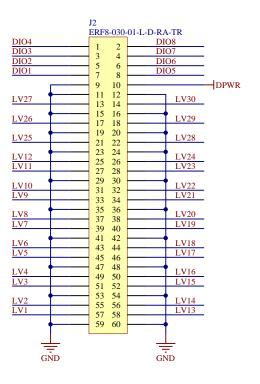

# LVBias/LVXBias Module

The low voltage bias module generates DC biases from -14.000V to +14.000V, with a resolution of about 1 mV. There are 24 low current biases (LV1-LV24, 10 mA max) and 6 high current biases (LV25-LV30, 500 mA max). The high current biases also have a programmable current limit (resolution of about 1 mA, minimum of 4 mA). Total current for the module can't exceed 1A. The voltage and current of each bias is monitored and reported. The capacitive load for each bias should be kept below 1 uF to guarantee amplifier stability.

There are optoisolators between each bias and the output connector. Initially, the optoisolators are open, and the pin on the output is connected to ground through a 100k resistor. When the system is commanded to enable power to the CCD, all biases are set to 0 V. The biases are checked, and then the optoisolators are closed. Next, each bias is set to its operating level in a user programmable sequence. At each step, the bias levels are checked before proceeding to the next step. The power down sequence proceeds in the reverse order.

The system supplies are continuously monitored in hardware by comparators. In the event a system supply leaves its normal operating range, all optoisolators to the CCD are opened.

The module also has 8 general purpose digital I/O lines, along with a digital power line. Each pair of I/O lines can be configured as inputs or outputs. The digital power line (DPWR) can either be driven externally by a 1.65 V to 5.5 V supply, or connected to an internal 3.3 V supply. Current draw from the internal power supply by external devices should be limited to 100 mA. By default, the DPWR line is set to be driven externally, and all I/O lines are configured as inputs. A user-programmable 16-bit 100 MHz CPU is available for simple digital I/O communication tasks. See the VCPU section for details.

The low voltage bias module requires the P17V and N17V system supplies. The low voltage bias module pinout is shown in Figure 20.

The LVXBias module has functionality and pinouts identical to the LVBias module, but is a longer card that only fits slots 3-4/9-12 and has additional buffering that accelerates the bias monitoring functions.

For firmware versions after 833, commands to change a bias can be given by the timing core. Bias changes commanded this way are ignored until the system has been configured and all biases have powered on. One bias command can be given per master clock cycle. It takes about 10 ms for a channel to settle to a new value. If too many bias commands are given too quickly, some will be ignored. Biases commanded this way are not as accurate as no corrections are performed. The output bias value will typically be within +/- 50 mV of the commanded value.

Figure 20: LVBias Module Connector

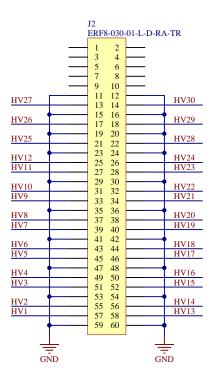

### **HVBias/HVXBias Module**

The high voltage bias module generates DC biases from 0.000V to +31.000V, with a resolution of about 1 mV. There are 24 low current biases (HV1-HV24, 10 mA max) and 6 high current biases (HV25-HV30, 250 mA max). The high current biases also have a programmable current limit (resolution of about 1 mA, minimum of 4 mA). Total current for the module can't exceed 1A. The voltage and current of each bias is monitored and reported. The capacitive load for each bias should be kept below 1 uF to guarantee amplifier stability.

There are optoisolators between each bias and the output connector. Initially, the optoisolators are open, and the pin on the output is connected to ground through a 100k resistor. When the system is commanded to enable power to the CCD, all biases are set to 0 V. The biases are checked, and then the optoisolators are closed. Next, each bias is set to its operating level in a user programmable sequence. At each step, the bias levels are checked before proceeding to the next step. The power down sequence proceeds in the reverse order.

The system supplies are continuously monitored in hardware by comparators. In the event a system supply leaves its normal operating range, all optoisolators to the CCD are opened.

The high voltage bias module requires the N6V, P17V, N17V and P35V system supplies. The high voltage bias module pinout is shown in Figure 21.

The HVXBias module has functionality and pinouts identical to the HVBias module, but is a longer card that only fits slots 3-4/9-12 and has additional buffering that accelerates the bias monitoring functions.

For firmware versions after 833, commands to change a bias can be given by the timing core. Bias changes commanded this way are ignored until the system has been configured and all biases have powered on. One bias command can be given per master clock cycle. It takes about 10 ms for a channel to settle to a new value. If too many bias commands are given too quickly, some will be ignored. Biases commanded this way are not as accurate as no corrections are performed. The output bias value will typically be within +/- 50 mV of the commanded value.

Figure 21: HVBias Module Connector

### **XVBias Module**

The XV bias module generates four DC biases from 0.000V to +91.000V and four DC biases from -95.000V to 0.000V with a resolution of about 2 mV. Each can supply 50 mA. The voltage and current of each bias is monitored and reported. The capacitive load for each bias should be kept below 0.1 uF to guarantee amplifier stability.

There are optoisolators between each bias and the output connector. Initially, the optoisolators are open, and the pin on the output is connected to ground through a 1M resistor. When the system is commanded to enable power to the CCD, all biases are set to 0 V. The biases are checked, and then the optoisolators are closed. Next, each bias is set to its operating level in a user programmable sequence. At each step, the bias levels are checked before proceeding to the next step. The power down sequence proceeds in the reverse order.

The system supplies are continuously monitored in hardware by comparators. In the event a system supply leaves its normal operating range, all optoisolators to the CCD are opened.

The XV bias module requires the P17V, N17V, P100V and N100V system supplies. This requires the use of an XV power supply and XV chassis. The XV bias module pinout is shown in Figure 22.

For firmware versions after 1090, commands to change a bias can be given by the timing core. Bias changes commanded this way are ignored until the system has been configured and all biases have powered on. One bias command can be given per master clock cycle to a P and/or N channel. It takes about 10 ms for a channel to settle to a new value. If too many bias commands are given too quickly, some will be ignored. Biases commanded this way are not as accurate as no corrections are performed. The output bias value will typically be within +/- 50 mV of the commanded value.

Figure 22: XVBias Module Connector

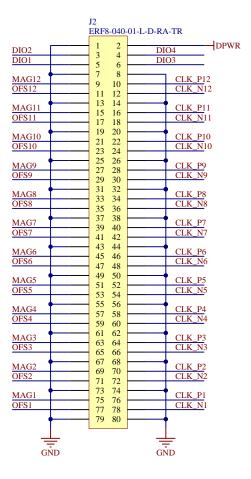

# HS (High Speed) Module

The high speed module outputs 12 high speed LVDS clocks with 1 ns timing resolution. The module also provides clock magnitudes adjustable from 5V to 14V with about 1 mV of resolution and capable of sourcing 1A. There are also clock offset voltages adjustable from -14 to +14V with about 1 mV of resolution and capable of sourcing/sinking 10 mA. The currents and voltages of each magnitude and offset are monitored. Together, each channel is intended to drive an LVDS receiver followed by a high speed clock buffer (such as an EL7457) that's AC-coupled to a CCD clock line. The clock buffer is powered by the channel magnitude. The CCD clock line is tied to the channel offset through a parallel diode and resistor. The diode direction is chosen based on whether the clock is normally high or low. The magnitude and offset are enabled and disabled at step 1 of the power sequence.

The module also has 4 general purpose digital I/O lines, along with a digital power line. Each I/O line can be configured as an input or output. The digital power line (DPWR) can either be driven externally by a 1.65 V to 5.5 V supply, or connected to an internal 3.3 V supply. Current draw from the internal power supply by external devices should be limited to 100 mA. By default, the DPWR line is set to be driven externally, and all I/O lines are configured as inputs. A user-programmable 16-bit 100 MHz CPU is available for simple digital I/O communication tasks. See the VCPU section for details.

The high speed module requires the P17V and N17V system supplies. The high speed module pinout is shown in Figure 23.

Figure 23: High Speed Module Connector

# **LVDS Module**

The LVDS module outputs 16 LVDS clocks with 10 ns timing resolution. The module also provides +3.3V, +/-5V, and +/-16V supplies (maximum current 1A each). The supplies are enabled and disabled at step 1 of the power sequence.

The module also has 4 general purpose digital I/O lines, along with a digital power line. Each I/O line can be configured as an input or output. The digital power line (DPWR) can either be driven externally by a 1.65 V to 5.5 V supply, or connected to an internal 3.3 V supply. Current draw from the internal power supply by external devices should be limited to 100 mA. By default, the DPWR line is set to be driven externally, and all I/O lines are configured as inputs. A user-programmable 16-bit 100 MHz CPU is available for simple digital I/O communication tasks. See the VCPU section for details.

The LVDS module requires the P6V, N6V, P17V and N17V system supplies. The LVDS module pinout is shown in Figure 24.

Figure 24 : LVDS Module Connector

# **Heater Module**

The heater module can drive two resistive heater elements (typically up to 25V at 1A each), and reads two temperature sensors. Power for the heater elements is drawn from the HEATER system supply, which should be a minimum of 2V higher than the maximum desired output voltage, but no greater than 36V.

The temperature sensing circuitry consists of two precision 10 uA current sources and two ADCs with high impedance instrumentation amplifier inputs. These are intended to be used with standard temperature sensing diodes such as the Lakeshore DT-670 with a four wire interface. The force lines (TEMPxF\_P and TEMPxF\_N) and sense lines (TEMPxS\_P and TEMPxS\_N) should be connected to the temperature sensor with shielded twisted pair. The positive lines (x\_P) should be connected to the temperature sensor anode, and the negative lines (x\_N) to the cathode. Interfacing with RTDs or other sensor types can be accommodated by customizing the gain and current source resistors on the heater module, and updating the firmware with the appropriate temperature curves. Each heater output can be forced to a constant voltage, or a target temperature can be set with a PID loop controlling the heater output. The heater output can be limited to a specified voltage to limit the output power. Upper and lower limits for valid sensor readings can be set. The heater output is disabled if these limits are exceeded.

Each heater PID loop is configured by setting P, I, D, and I Limit terms, and specifying which temperature sensor to close the loop around. A target temperature is given. A PID loop update time is also defined. Internally, the PID loop calculates an error signal by subtracting the current temperature from the target temperature. Once per update loop, the P term is multiplied by the current error, the I term is multiplied by a running sum of the errors (limited to I Limit), and the D term is multiplied by the difference between this error and the last. The sum of these results is then translated into a linear power output to the heater. The loop update time should be set to a timescale comparable to how long it takes the system to show a response to an input. If ramping is enabled for a heater, the PID loop target begins at the current temperature, and linearly ramps to the final target temperature at the configured rate.

The module also has 8 general purpose digital I/O lines, along with a digital power line. Each pair of I/O lines can be configured as inputs or outputs. The digital power line (DPWR) can either be driven externally by a 1.65 V to 5.5 V supply, or connected to an internal 3.3 V supply. Current draw from the internal power supply by external devices should be limited to 100 mA. By default, the DPWR line is set to be driven externally, and all I/O lines are configured as inputs. A user-programmable 16-bit 100 MHz CPU is available for simple digital I/O communication tasks. See the VCPU section for details.

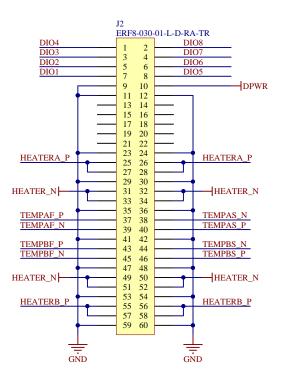

The heater module requires the P17V and HEATER system supplies. The heater module pinout is shown in Figure 25.

Figure 25: Heater Module Connector

# **HeaterX Module**

The HeaterX module (an upgrade of the standard Heater module) can drive two resistive heater elements (typically up to 25V at 1A each), and reads three temperature sensors. Power for the heater elements is drawn from the HEATER system supply, which should be a minimum of 2V higher than the maximum desired output voltage, but no greater than 36V.

The temperature sensing circuitry consists of three precision current sources programmable from 25 nA to 1.5 mA in 25 nA steps, and three ADCs with high impedance inputs. They are intended to be used with standard temperature sensing diodes such as the Lakeshore DT-670 with a four wire interface, or with standard 100 or 1000 Ohm RTDs. The force lines (TEMPxF\_P and TEMPxF\_N) and sense lines (TEMPxS\_P and TEMPxS\_N) should be connected to the temperature sensor with shielded twisted pair. The positive lines (x\_P) should be connected to the temperature sensor anode, and the negative lines (x\_N) to the cathode. Interfacing with other sensor types can be accommodated by updating the firmware with the appropriate temperature curves. Each heater output can be forced to a constant voltage, or a target temperature can be set with a PID loop controlling the heater output. The heater output can be limited to a specified voltage to limit the output power. Upper and lower limits for valid sensor readings can be set. The heater output is disabled if these limits are exceeded.

Each heater PID loop is configured by setting P, I, D, and I Limit terms, and specifying which temperature sensor to close the loop around. A target temperature is given. A PID loop update time is also defined. Internally, the PID loop calculates an error signal by subtracting the current temperature from the target temperature. Once per update loop, the P term is multiplied by the current error, the I term is multiplied by a running sum of the errors (limited to I Limit), and the D term is multiplied by the difference between this error and the last. The sum of these results is then translated into a linear power output to the heater. The loop update time should be set to a timescale comparable to how long it takes the system to show a response to an input. If ramping is enabled for a heater, the PID loop target begins at the current temperature, and linearly ramps to the final target temperature at the configured rate.

The module also has 8 general purpose digital I/O lines, along with a digital power line. Each pair of I/O lines can be configured as inputs or outputs. The digital power line (DPWR) can either be driven externally by a 1.65 V to 5.5 V supply, or connected to an internal 3.3 V supply. Current draw from the internal power supply by external devices should be limited to 100 mA. By default, the DPWR line is set to be driven externally, and all I/O lines are configured as inputs. A user-programmable 16-bit 100 MHz CPU is available for simple digital I/O communication tasks. See the VCPU section for details.

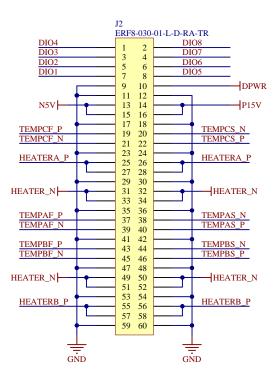

The HeaterX module requires the P17V, N6V and HEATER system supplies. The heater module pinout is shown in Figure 26.

Figure 26: HeaterX Module Connector

# **System Power**

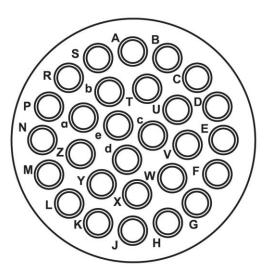

Power is supplied to a standard Archon system through a Souriau 28-pin UT002028PH circular connector (Figure 27).

#### Figure 27: Power Connector

| Pin        | Voltage                     | Power Good Range          |

|------------|-----------------------------|---------------------------|

| A, C, T, V | +2.5 V Digital              | +2.1 V +2.9 V             |

| B, D, U, W | +2.5 V Digital Return       |                           |

| E, G       | +5 V Digital                | +4.4 V +5.6 V             |

| F, H       | +5 V Digital Return         |                           |

| J          | +6 V Analog                 | +5.5 V +6.6 V             |

| К          | +6 V / -6 V Analog Return   |                           |

| L          | -6 V Analog                 | -5.3 V6.6 V               |

| Μ          | +17 V Analog                | +16.4 V +17.5 V           |

| Ν          | +17 V / -17 V Analog Return |                           |

| Р          | -17 V Analog                | -16.6 V17.7 V             |

| R          | +35 V Analog                | +34.3 V +36.0 V           |

| b          | +35 V / -35 V Analog Return |                           |

| S          | -35 V Analog                | -33.8 V35.9 V             |

| Х          | Heater                      | +18.0 V +36.0 V           |

| Υ          | Heater Return               |                           |

| Z          | User                        | +18.0 V +36.0 V           |

| а          | User Return                 |                           |

| С          | Fan (+12 V)                 | Directly connected to fan |

| d          | Fan Return                  |                           |

| е          | Earth ground                |                           |

| Pin          | Voltage                      | Power Good Range          |

|--------------|------------------------------|---------------------------|

| A, C, T, V   | +2.5 V Digital               | +2.1 V +2.9 V             |

| B, D, U, W   | +2.5 V Digital Return        |                           |

| E, G         | +5 V Digital                 | +4.4 V +5.6 V             |

| F <i>,</i> H | +5 V Digital Return          |                           |

| J            | +6 V Analog                  | +5.5 V +6.6 V             |

| К            | +6 V / -6 V Analog Return    |                           |

| L            | -6 V Analog                  | -5.3 V6.6 V               |

| Μ            | +17 V Analog                 | +16.4 V +17.5 V           |

| Ν            | +17 V / -17 V Analog Return  |                           |

| Р            | -17 V Analog                 | -16.6 V17.7 V             |

| R            | +35 V Analog                 | +34.3 V +36.0 V           |

| b            | +35 V / -35 V Analog Return  |                           |

| S            | -100 V Analog                | -97 V103 V                |

| Х            | Heater                       | +18.0 V +36.0 V           |

| Y            | Heater Return                |                           |

| Z            | +100 V Analog                | +97 V +103 V              |

| а            | +100 V / -100V Analog Return |                           |

| с            | Fan (+12 V)                  | Directly connected to fan |

| d            | Fan Return                   |                           |

| е            | Earth ground                 |                           |

|              |                              |                           |

The XV power supply and XV chassis use a modified pinout, shown below.

The Archon AC chassis only requires a standard IEC AC power cable, and 110/220V AC power.

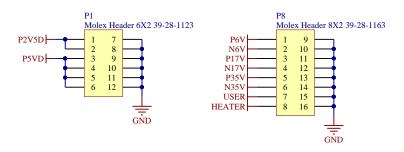

Only the voltages used by the installed modules need be supplied. The backplane always requires the +2.5 V and +5 V digital supplies. Power from the circular connector is routed to a power board. This board monitors the system supply voltages. When all supply voltages are at their nominal levels, the power is connected to the rest of the system through solid state relays. The allowed nominal levels are set by resistors on the power board, and the default power good ranges are shown in the power cable pinout. Switches must be set on P1 and P7 on the power board to indicate which supply voltages are being used in the system. The power good connector pinout is shown in Figure 28. Set the respective switches to ON to indicate a supply is in use and should be monitored.

Figure 28: Power Monitor Switches

The XV chassis has a modified set of switches, as shown in Figure 29.

Figure 29: XV Power Monitor Switches

In addition, all of the system supply voltages and currents are monitored and digitized. These values are retrieved by the backplane over a cable connected to P9. This connector also carries the system-wide Power Good signal.

The standard Archon power supply is shown in Figure 30. It uses low noise switching supplies to generate +2.5V, +5V, +6V, -6V, +17V, -17V, and +35V voltages, along with +12V fan and +28V heater voltages. It accepts 100-240VAC at 50/60Hz, and is typically 61% efficient. Its dimensions are 8" x 6" x 4.5" (20.32cm x 15.24cm x 11.43cm), and it weighs 4.5 pounds (2.1 kg). The XV power supply has the same dimensions, but adds +100V and -100V voltages. The Archon AC chassis needs no external power supply, and can optionally have +/-100V supplies installed.

Figure 30: Archon Power Supply

# **Power Consumption**

The following table lists the approximate current required from the system supplies for various configurations. These currents do not include any loads external to the controller (current supplied to CCD output FETs, current required to clock capacitve loads, heater current, etc). Enabled biases are set to 50% of their maximum values, and clocks are set to 0V. The typical systems contain 1 LVBias module, 1 HVBias module, 3 Driver modules, 1 Heater module, and either 1 or 4 AD modules.

| Configuration          | +2.5V (A) | +5V (A) | +/-6V (A) | +/-17V (A) | +35V (A) |

|------------------------|-----------|---------|-----------|------------|----------|

| Backplane alone        | 2.2       | 0.8     |           |            |          |

| LVBias, no HC enabled  | 2.2       | 1       |           | 0.05       |          |

| LVBias, all HC enabled | 2.2       | 1       |           | 0.1        |          |

| HVBias, no HC enabled  | 2.2       | 1       | 0.02      | 0.03       | 0.04     |

| HVBias, all HC enabled | 2.2       | 1       | 0.06      | 0.03       | 0.09     |

| Driver, no channels    | 2.2       | 1       |           |            |          |

| Driver, all channels   | 2.2       | 1.1     | 0.06      | 0.09       |          |

| AD, no channels        | 2.2       | 1.1     | 0.03      |            |          |

| AD, all channels       | 3         | 1.1     | 0.12      |            |          |

| Heater                 | 2.2       | 1       |           |            |          |

| Typical 4 channel      | 3.5       | 2.6     | 0.33      | 0.36       | 0.09     |

| Typical 16 channel     | 6.3       | 3.4     | 0.7       | 0.39       | 0.09     |

The total typical DC power required for the 4 channel system is 41 W. The 16 channel system requires 58 W. The AC power consumption at the wall is the listed power divided by the efficiency of the Archon power supply (~61%). A typical 16 channel Archon AC chassis draws 89W at the wall in full operation.

# Communication

All communication between the host system and the Archon controller is over the gigabit Ethernet interface. By default, the controller listens for a TCP/IP connection at address 10.0.0.2 on port 4242 (the host is usually set to 10.0.0.1). To change the IP address, connect to Archon using the GUI. Set the new, desired IP address at the bottom left of the System tab and click "Apply Network Configuration" (there will be error messages because Archon is no longer responding on the old address). Click Disconnect, change the Archon IP address at the top left to the new address, and click Connect. Select System->Flash Active Config to make this change permanent.

The controller only responds to commands, it never initiates a message. Commands to the controller are of the form:

#### >xxCOMMAND

The command begins with a greater-than symbol, followed by a two hexadecimal digit reference number, followed by the command itself, and terminated with a newline (n / ASCII 10 / 0x0A).

Unrecognized commands are ignored. In the event of an error parsing or executing a command, the response from the controller will be:

#### ?xx

The initial '?' indicates an error occurred processing the command. The two hexadecimal digit reference number matching what was sent with the command follows. The response is terminated with a newline.

On success, the controller will respond:

#### <xxRESPONSE

The initial '<' indicates success. The two hexadecimal digit reference number matching what was sent with the command follows. The text of the response (if any) is next, and the response is terminated with a newline.

To conserve bandwidth, certain commands request the return of raw binary data (such as fetching the contents of a frame buffer). In these cases, the response takes the following form:

#### <xx:bbbbb...bbbbb

The initial '<' indicates success. The two hexadecimal digit reference number matching what was sent with the command follows. The ':' indicates a binary response. The remainder of the response is 1024 bytes of raw binary data, with no terminating newline.

The list of controller commands follows.

## **SYSTEM**

Reports the system configuration (installed modules, firmware versions, etc). The response is a sequence of KEY=VALUE pairs separated by spaces and terminated with a newline. The list of keys returned follows.

| BACKPLANE_REV=n                               | <pre>; n = 1 for an X12 backplane, n = 2 for X16<br/>; Backplane PCB revision, 0 = A, 1 = B<br/>; Backplane firmware, major.minor.build</pre> |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| BACKPLANE_ID=x<br>MOD_PRESENT=x               | ; 16 hexadecimal digit backplane unique ID<br>; Hexadecimal bit field: a 1 in the LSB                                                         |

| MODn_TYPE=n                                   | <pre>; indicates a module is present in slot 1 ; Reports module type for slots 1n. ; 0: None</pre>                                            |

|                                               | ; 1: Driver<br>; 2: AD                                                                                                                        |

|                                               | ; 3: LVBias<br>; 4: HVBias                                                                                                                    |

|                                               | ; 5: Heater<br>; 7: HS<br>; 8: HVXBias                                                                                                        |

|                                               | ; 9: LVXBias<br>; 10: LVDS                                                                                                                    |

|                                               | ; 11: HeaterX<br>; 12: XVBias                                                                                                                 |

|                                               | ; 13: ADF<br>; 14: ADX                                                                                                                        |

|                                               | ; 15: ADLN<br>; 16+: Unknown<br>; Module m PCB revision, 0 = A, 1 = B                                                                         |

| MODn_REV=n<br>MODn_VERSION=n.n.n<br>MODn_ID=x | ; Module m FCB revision, 0 = A, I = B<br>; Module m firmware, major.minor.build<br>; 16 hexadecimal digit module m unique ID                  |

# **STATUS**

Reports the system status. The response is a sequence of KEY=VALUE pairs separated by spaces and terminated with a newline. The list of keys returned follows.

| VALID=n<br>COUNT=n                                                                                                                                                       | ; n = 1 if remaining status fields are valid<br>; Number of times system status has been                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOG=n<br>POWER=n                                                                                                                                                         | <pre>; updated<br/>; Number of log entries available<br/>; Power status. Possible values:<br/>; 0: Unknown - usually an internal error<br/>; 1: Not Configured - no configuration applied<br/>; 2: Off - power to the CCD is off<br/>; 3: Intermediate - some modules have enabled<br/>; power to the CCD, some have not</pre>                                                                                                                                                                                                                                    |

|                                                                                                                                                                          | ; 4: On – Power to the CCD is on<br>; 5: Standby – System is in standby                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OVERHEAT=n<br>BACKPLANE_TEMP=f<br>P2V5_V=f<br>P2V5_I=f<br>P5V_V=f<br>P6V_V=f<br>P6V_V=f<br>N6V_V=f<br>N6V_I=f<br>N6V_I=f<br>P17V_V=f<br>P17V_V=f<br>N17V_V=f<br>N17V_V=f | <pre>; n = 1 when system is overheating<br/>; Floating point backplane temperature in C<br/>; +2.5V system supply voltage in V<br/>; +2.5V system supply current in A<br/>; +5V system supply voltage in V<br/>; +5V system supply current in A<br/>; +6V system supply voltage in V<br/>; +6V system supply voltage in V<br/>; -6V system supply voltage in V<br/>; -6V system supply voltage in V<br/>; +17V system supply voltage in V<br/>; +17V system supply current in A<br/>; -17V system supply voltage in V<br/>; -17V system supply current in A</pre> |

| P35V_V=f<br>P35V_I=f<br>N35V_V=f<br>P100V_V=f<br>P100V_I=f<br>N100V_I=f<br>N100V_I=f<br>USER_V=f<br>USER_I=f<br>HEATER_V=f<br>HEATER_I=f<br>FANTACH=n                    | <pre>; +35V system supply voltage in V<br/>; +35V system supply current in A<br/>; -35V system supply voltage in V<br/>; -35V system supply current in A<br/>; +100V system supply voltage in V<br/>; +100V system supply current in A<br/>; -100V system supply voltage in V<br/>; -100V system supply current in A<br/>; User system supply voltage in V<br/>; User system supply current in A<br/>; Heater system supply voltage in V<br/>; Heater system supply current in A<br/>; Fan speed in RPM (Rev F only)</pre>                                        |

| MODm/TEMP=f<br>MODm/LVLC_Vn=f                                                                                                         | ; Floating point module m temperature in C<br>; LV(X)Bias only: Floating point module m low<br>; voltage low current n voltage reading in V<br>; n = 1 to 24 maps to LV1 to LV24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODm/LVLC_In=f                                                                                                                        | ; LV(X)Bias only: Floating point module m low<br>; voltage low current n current reading in mA<br>; n = 1 to 24 maps to LV1 to LV24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MODm/LVHC_Vn=f                                                                                                                        | ; LV(X)Bias only: Floating point module m low<br>; voltage high current n voltage reading in V<br>; n = 1 to 6 maps to LV25 to LV30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MODm/LVHC_In=f                                                                                                                        | ; LV(X)Bias only: Floating point module m low<br>; voltage high current n current reading in mA<br>; n = 1 to 6 maps to LV25 to LV30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MODm/HVLC_Vn=f                                                                                                                        | <pre>; HV(X)Bias only: Floating point module m high<br/>; voltage low current n voltage reading in V<br/>; n = 1 to 24 maps to HV1 to HV24</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MODm/HVLC_In=f                                                                                                                        | <pre>; HV(X)Bias only: Floating point module m high<br/>; voltage low current n current reading in mA<br/>; n = 1 to 24 maps to HV1 to HV24</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |