SEMICONDUCTOR TECHNOLOGY ASSOCIATES

# STA4850 4080 X 4080 Pixel CCD Image Sensor

#### **Features**

Format: 4080 x 4080 pixels Pixel size:  $15 \times 15$  um 100% fill factor Readout noise:  $\leq 3 e^-$  RMS at 100 kHz Full well capacity:  $>200 ke^-$ Output speed: 100 kHz - 1 MHzOutput sensitivity:  $4 uV/e^-$ 3 phase parallel and serial operation Coupled quadrant structure Any 1, 2, or 4 outputs Back illuminated Thermal time constant: ~200 s Thermal stability: <1 mKSubstrate thickness: 30 or 100 um

### **Description**

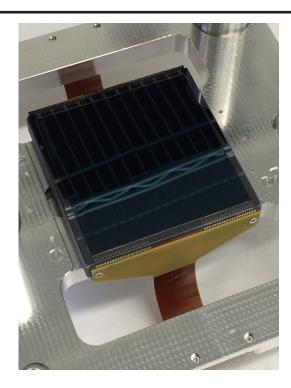

The STA4850 is a 4080 X 4080 pixel buried channel Charge Coupled Device (CCD) sensor intended for use in high-resolution scientific, space-based, industrial, and commercial electro-optical systems. The CCD is organized in four coupled symmetric quadrants each containing an array of 2040 horizontal by 2040 vertical pixels. The pixel geometry is 15 um square. The coupled symmetric design and single stage output structure allows full frame low noise operation through one, two, or four outputs.

The packaged device is offered back illuminated with a variety of anti-reflection (AR) coating options and includes an integrated temperature sensor, heater, and JFET buffer.

The CCD package is designed for ultra high stability applications including interferometry and high resolution planet finding spectroscopy. It is made of high conductivity low thermal expansion AlSi alloy (CE6F) allowing short thermal time constants, and with the integrated sensor and heater, has the best temperature uniformity and stability ever offered in a CCD of this size. It can be mounted in one of three ways and included with an optional radiation shield, thermal isolator, and warm mounting ring. The radiation shield also doubles as a device handling jig.

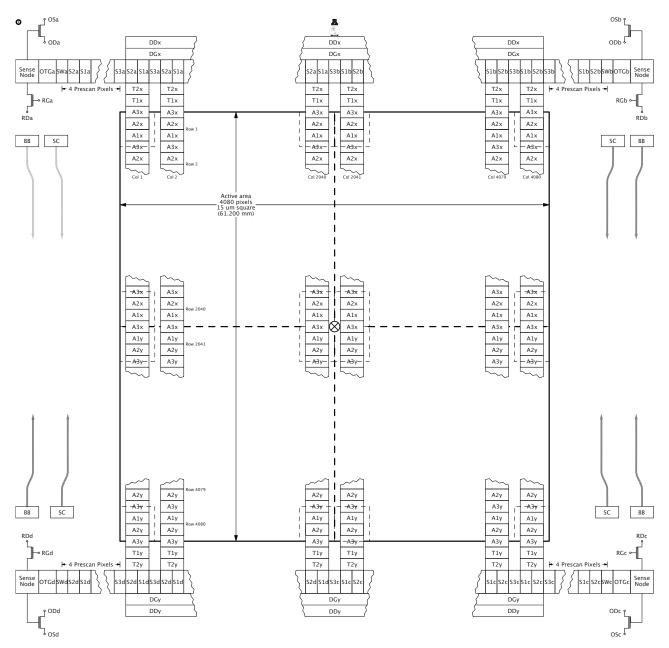

### **Functional Description**

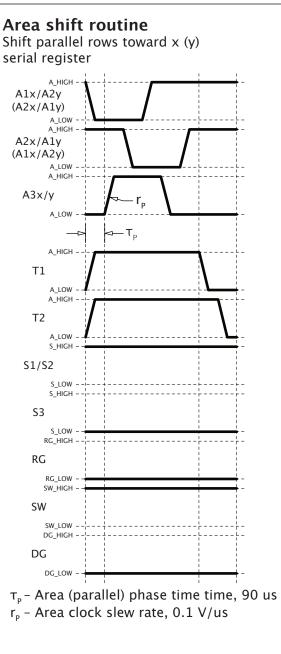

The CCD serial (Sn) and area (An) gates are arranged such that an identical clocking pattern to each of the four quadrants results in standard four output operation.

Modification of the basic area clock pattern allows charge to be shifted up, down, or held in each of the two area clock regions independently. Modification of the basic serial clock pattern allows charge to be shifted left, right, or held in each of the four serial register regions independently. Full frame single amplifier operation is possible from any output, and full frame dual amplifier operation is possible from any pair of outputs.

# STA4850

The serial register pixels have approximately twice the capacity of each area pixel allowing for efficient area charge binning operation. The SG pixel is approximately twice the size of the other serial register pixels (four times the capacity of an area pixel) to allow efficient serial binning.

For optimum PRNU along the device centerlines, it is suggested that integration occur under the A1 and A2 phases (A1 and A2 high). Charge is then shifted to the serial register in order, A1/T1 to A2/T2 to A3/S1/S2.

The dual transfer gate structure allows for stable serial readout during parallel clocking. This in turn allows for maximum pCTE with minimum overhead.

A dump drain and gate is included to allow fast array flushing and mitigate horizontal blooming from

STA4850 Functional Diagram

localized bright sources or defects.

Scupper regions around the image area absorb excess dark current near the edges and improve the uniformity of the DSNU structure.

Backside bias is available primarily to limit charge diffusion on 100 um thick devices.

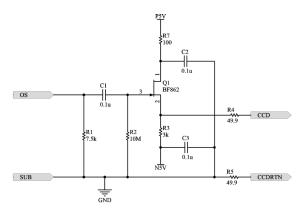

All four outputs are of identical design. Each is a single stage NMOS source follower that have proven low noise performance with a 1/f corner frequency below 100 kHz. Their output impedance is about 3 kohm, but the typical package includes AC coupling and a low noise JFET source follower stage which operates at the CCD package temperature. This structure is capable, depending on output speed, of driving cabling up 1–2 m in length with minimal noise impact.

### **Operating point**

These are nominal conditions, each device is optimized individually prior to performance characterization.

|                                               |                          | Range |      |     |      |                                                                                                      |

|-----------------------------------------------|--------------------------|-------|------|-----|------|------------------------------------------------------------------------------------------------------|

| Name                                          | Symbol                   | Min   | Тур  | Max | Unit | Remarks                                                                                              |

| DC CHARACTERISTICS                            |                          |       |      |     |      |                                                                                                      |

| Output Drain voltage                          | OD                       | 15    | 24   | 30  | v    | Must be 5–10 V greater than<br>RD                                                                    |

| DC reset drain voltage                        | RD                       | 10    | 15   | 20  | V    | Must be 5–10 V less than OD                                                                          |

| DC output transfer gate<br>voltage            | OTG                      | -5    | -1   | 5   | v    |                                                                                                      |

| DC substrate ground voltage                   | SS                       |       | 0    |     |      |                                                                                                      |

| DC scupper voltage                            | SC                       |       | 20   |     | v    | Guard ring to absorb charge produced outside the image area                                          |

| DC dump drain voltage                         | DD                       |       | 20   |     | V    |                                                                                                      |

| DC Backside bias voltage                      | BB                       |       | -30  | 0   | v    | Limits charge diffusion in 100<br>um thick Si. <b>Should be 0 V on</b><br><b>30 um thick Silicon</b> |

| Output load                                   | Z <sub>LOAD</sub>        |       | 7.5  |     | kΩ   |                                                                                                      |

| CLOCK CHARACTERISTICS                         |                          |       |      |     |      |                                                                                                      |

| Serial (horizontal) register<br>clock voltage | S1, S2,<br>S3            | -5    |      | 5   | V    | Typical                                                                                              |

| Summing well clock voltage                    | SW                       | -5    |      | 5   | V    | Typical                                                                                              |

| Parallel (vertical) area clock<br>voltage     | A1, A2,<br>A3, T1,<br>T2 | -9    |      | 3   | v    | Typical                                                                                              |

| Reset gate clock voltage                      | RG                       | -3    |      | 10  | V    | Typical                                                                                              |

| Dump gate voltage                             | DG                       | 1     |      | 4   | V    | Typical                                                                                              |

| Operating temperature                         | T <sub>CCD</sub>         | -110  | -100 | +40 | °C   |                                                                                                      |

### Performance specifications

A complete test report is delivered with each supplied device. All device specification correspond to the same operating point which is supplied with the test report.

|                                   |                 | Range |     |      |          |                             |

|-----------------------------------|-----------------|-------|-----|------|----------|-----------------------------|

| Name                              | Symbol          | Min   | Тур | Max  | Unit     | Remarks                     |

| PHOTO RESPONSE                    |                 |       |     |      |          |                             |

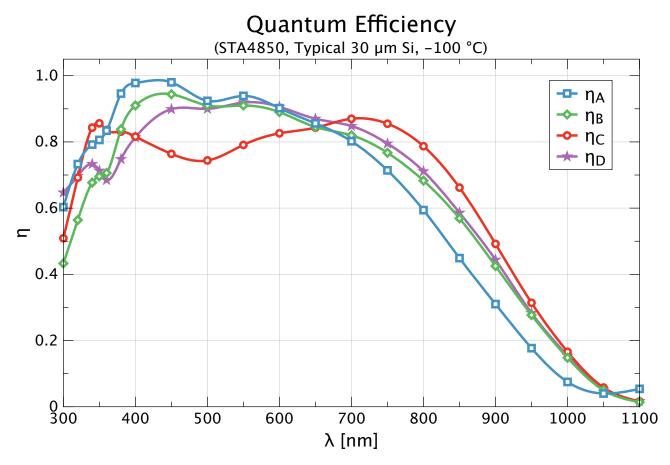

| Quantum efficiency                |                 |       | >90 |      | %        | At 550 nm, see figure       |

| Photo response non–<br>uniformity | PRNU            |       |     | 10   | %        |                             |

| Dark current                      |                 |       | 2.9 | 5.0  | e⁻/pix/h | $T_{CCD} = -100 \text{ °C}$ |

| DYNAMIC RESPONSE                  |                 |       |     |      |          |                             |

| Image pixel capacity              | FWC             | 200   |     |      | ke⁻      |                             |

| Serial pixel capacity             |                 | 200   |     |      | ke⁻      |                             |

| Output node capacity              |                 | 200   |     |      | ke⁻      |                             |

| Readout noise                     | RN              |       | 3   | 4    | e⁻       |                             |

| Non-linearity                     | RNL             |       | 2   |      | %        | Up to FWC                   |

| Amplifier sensitivity             |                 |       | 4   |      | uV/e⁻    |                             |

| DC output level                   | V <sub>os</sub> |       | 16  |      | V        |                             |

| CHARGE TRANSFER                   |                 |       |     |      |          |                             |

| Serial ineffiency                 | sCTI            |       |     | 1e-5 |          | Per pixel                   |

| Parallel inefficiency             | рСТІ            |       |     | 1e-5 |          | v                           |

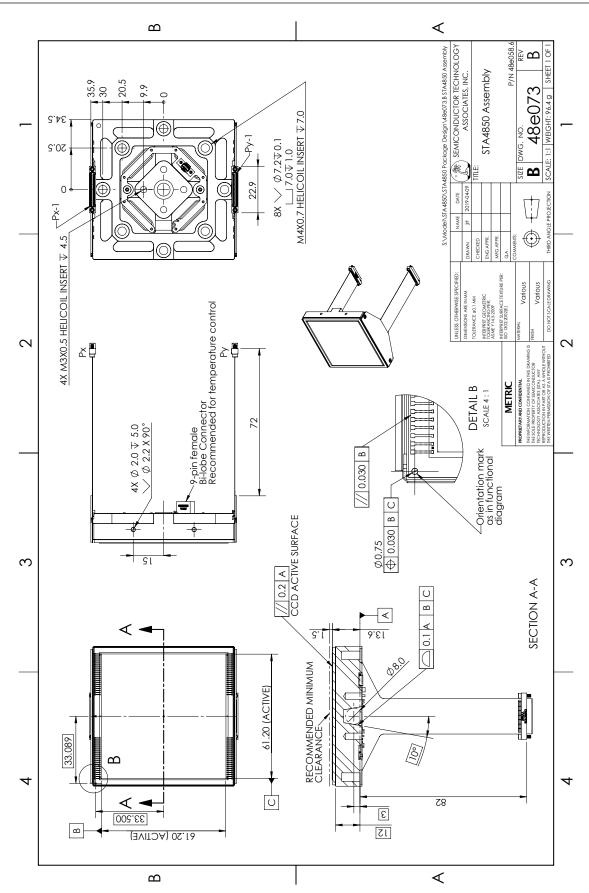

### Mounting

The STA4850 package is designed to be mounted in one of three manners according to different end uses or preferences.

- A thermal isolator can be directly attached to the CCD package for minimum thermal mass and better thermal control in high stability applications. That isolator can be trimmed on a per device basis to level and space the CCD relative to warm mounting points.

- Device specific shims and studs can be installed in a three point nearly-symmetric pattern to level the device relative to a cold mounting surface. This traditional mounting method works well for device interchageability, but is not particularly well suited for high precision applications.

- A unique ball-in-cone or cone-in-cone mount can be used to kinematically constrain the CCD center in 3 or 5 degrees of freedom respectively. The remaining 3 or 1 degrees of freedom are then constrained with flexures attached to the edge features, while the cold thermal sink attaches in four positions near the center of each CCD quadrant. This method is ideal for ultra high precision applications like high resolution radial velocity spectrometers.

## Data Sheet

### STA4850

### STA4850

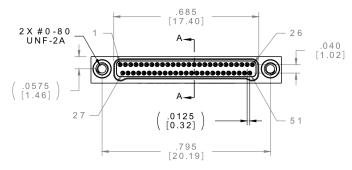

Omnetics A28300-051 51-pin male Bi-Lobe connector

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Pin                                                                                                                                                                                                                       | Signal                                                                                                                                                                                                                                                                                                                                                              | Pin                                                                                                                                          | Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$  | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>23<br>24<br>22<br>22<br>22<br>22<br>24<br>25 | $\begin{array}{c} T1x \ (y)^{\dagger}\\ T2x \ (y)^{\dagger}\\ ODb \ (d)\\ RDb \ (d)\\ OTGb \ (d)\\ OTGb \ (d)\\ CCDb \ (d)\\ CCDRTNb \ (d)\\ CCDRTNb \ (d)\\ GND\\ DGx \ (y)\\ DDx \ (y)\\ SC\\ N5V\\ PSV\\ BB\\ DDx \ (y)\\ DGx \ (y)\\ DGx \ (y)\\ GND\\ CCDa \ (c)\\ CCDRTNa \ (c)\\ GND\\ OTGa \ (c)\\ RDa \ (c)\\ DDa \ (c)\\ T2x \ (y)^{\dagger} \end{array}$ | 27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50 | $\begin{array}{c} & A1x \; (y)^{\dagger} \\ & A2x \; (y)^{\dagger} \\ & A2x \; (y)^{\dagger} \\ & A3x \; (y)^{\dagger} \\ & GND \\ & RGb \; (d) \\ & S1b \; (d) \\ & S1b \; (d) \\ & S2b \; (d) \\ & S3b \; (d) \\ & HEATERx+ \; (y+)^{*} \\ & RTDIx+ \; (y+)^{*} \\ & RTDIx- \; (y-)^{*} \\ & RTDVx- \; (y-)^{*} \\ & RTDVx- \; (y-)^{*} \\ & RTDVx+ \; (y+)^{*} \\ & HEATERx- \; (y-)^{*} \\ & S3a \; (c) \\ & S2a \; (c) \\ & S1a \; (c) \\ & SVa \; (c) \\ & RGa \; (c) \\ & GND \\ & A3x \; (y)^{\dagger} \\ & A2x \; (y)^{\dagger} \end{array}$ |

- \* This feature is untested and not recommended for use. Please, leave floating.

- <sup>+</sup> A1, A2, A3, T1, and T2 are connected a/b (c/d) through polysilicon.

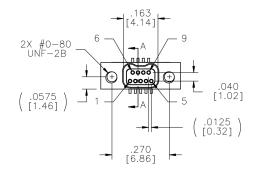

Omnetics A29200-009 9-pin female Bi-Lobe connector

| Pin                   | Signal                                      |

|-----------------------|---------------------------------------------|

| 1<br>2<br>3<br>4      | HEATER-                                     |

| 5<br>6<br>7<br>8<br>9 | HEATER+<br>RTDV+<br>RTDV-<br>RTDI-<br>RTDI+ |

Heater: 100 ohm, 6.25 W, 25 V max. RTD: 1 kOhm, Pt

CCDn pin is connected to the CCD output source (OS) pin with buffered AC coupling.

Data Sheet

#### Read pixel routine

Shift serial pixels toward a/d (b/c) output and read.

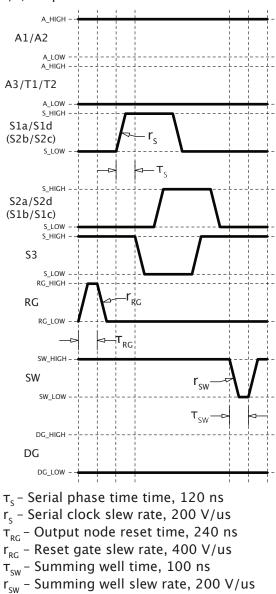

### Timing

A fast flush pixel routine is based on the read pixel routine but clocks SW the same as S3 and holds RG high during serial clocking.

A variant of the read pixel or fast flush pixel routines is usually implemented as the integration delay loop. During integration DG is typically held high.

STA recommends flushing the serial register during integration and prior to frame readout.

For high stability applications where precision temperature control (< 1 mK) is required, it is possible to shuffle charge between the A1 and A2 phases during integration by adding them to the delay loop. This makes the mean power dissipation constant.

### **Quantum Efficiency**

The STA4850 can be fabricated on either 30 um or 100 um thick silicon. The latter has a higher red quantum efficiency (QE). The sensor can be coated with user specified anti-reflection (AR) coatings. Typically the thinner CCD is supplied with a broadband optimized coating while the thicker is supplied with a red optimized AR coating.

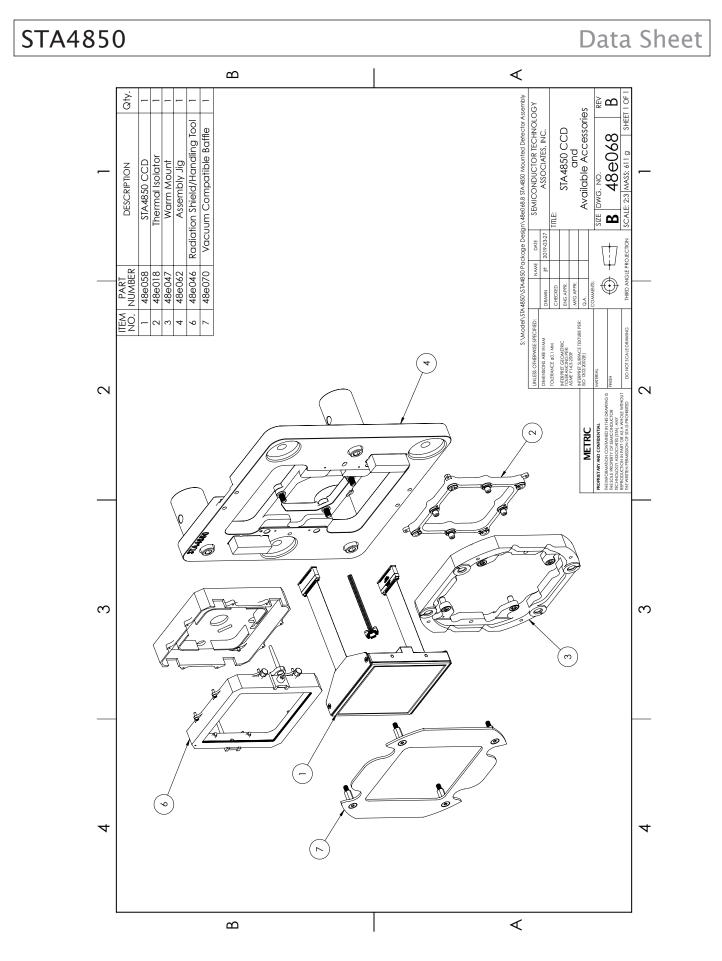

#### Accessories

The STA4850 can be supplied as a bare or packaged CCD, with various accessories, or as a complete cryogenically cooled camera system with Archon controller. Solid models for all items are available to customers upon request.

- 48e016 Upper radiation shield and handling jig

- 48e018 Thermal isolator assembly

- 48e046 Radiation shield assembly

- 48e047 Rectangular warm mount

- 48e062 Assembly tool

### **Cosmetic Grading**

STA4850 CCDs are graded according to cosmetic defects, but custom grades are available upon request.

### Data Sheet

| Specification  | Grade | Range |      | Remarks                                              |  |

|----------------|-------|-------|------|------------------------------------------------------|--|

| specification  | Grade | Тур   | Max  | Remarks                                              |  |

| Column Defects | A     | 0     | 5    |                                                      |  |

|                | В     | <5    | 10   | An image column with >20 contiguous hot or dark      |  |

|                | С     | <10   | 15   | pixels.                                              |  |

|                | ENG   | >15   |      |                                                      |  |

| Hot pixels     | A     | <300  | 500  |                                                      |  |

|                | В     | <500  | 800  | A pixel with dark current generation of 5 e-/pixel/s |  |

|                | с     | <1000 | 1500 | at –100 degC.                                        |  |

|                | ENG   | >1500 |      |                                                      |  |

| Dark pixels    | A     | <200  | 400  |                                                      |  |

|                | В     | <700  | 800  | A pixel with photo-response at 532 nm of <50% of     |  |

|                | с     | <800  | 1000 | the local mean.                                      |  |

|                | ENG   | >1000 |      |                                                      |  |

| Trap           | A     | <5    | 10   |                                                      |  |

|                | В     | <10   | 15   | A pixel that temporarily holds more than 200 e- of   |  |

|                | С     | <15   | 20   | charge.                                              |  |

|                | ENG   | >20   |      |                                                      |  |

### Warranty

Semiconductor Technology Associates, Inc. (STA) will repair or replace, at our option, any image sensor product within twelve months of delivery to the end customer, for any defect in materials or workmanship. Contact STA for further warranty information, a return number, and shipping instructions.

#### Certification

Semiconductor Technology Associates, Inc. (STA) certifies that all products are carefully inspected and tested prior to shipment and will meet all of the specification requirements under the performance specifications summarized.v